### Network Research Exhibition: November, 2025

# Case Study for Data-Intensive Traffic from Vera Rubin Observatory Supported by Path Aware PolKA Network

Magnos Martinello<sup>1</sup>

Rafael Guimarães<sup>2</sup>

Everson Borges<sup>2</sup>

Daniel

Ventorim<sup>12</sup>

Cristina Dominicini<sup>2</sup>

Moises R. N. Ribeiro<sup>1</sup>

Harvey B. Newman<sup>3</sup>

Jeronimo Bezerra<sup>4</sup>

# Agenda

- Motivation

- Proposal

- Design

- Prototype

- Applications

- Conclusions and future works

Global Network Advancement Group (GNA-G) mission:

to enable ultra-fast, resilient, and adaptive data paths for Data-Intensive Science

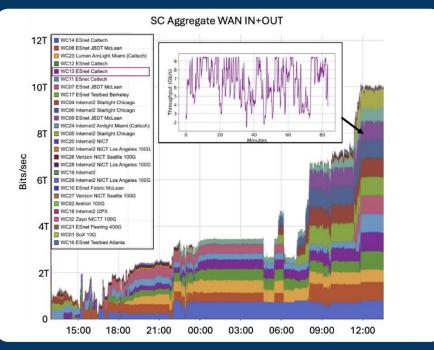

# Data Intensive Science Requirements

- High Performance WANs

- Big Data Flows

- High throughput over long distances

- Global Network Advancement Group (GNA-G) mission: to enable ultra-fast, resilient, and adaptive data paths for Data-Intensive Science

- SDN and Network Programmability

- Innovation of protocols

- SDN and Programmable Network Devices:

- Innovation and custom protocols.

- The packet forwarding based on table lookups has some bottlenecks:

Large number of states

Limited capacity of switch tables

Latency for path configuration

Network scalability

Granularity

**Agility**

- SDN and Programmable Network Devices:

- Innovation and custom protocols.

- Bottleneck: forwarding based on table entries

Large number of states

Limited capacity of switch tables

Latency for path configuration

Network scalability

Granularity

Agility

What are the alternatives to tackle these problems?

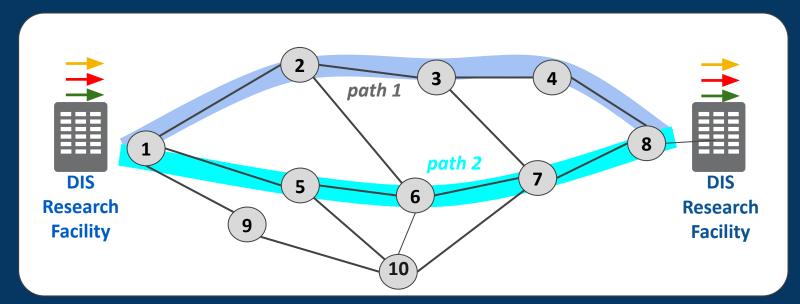

- Source Routing (SR):

- A source specifies a path and adds a route label to the packet header.

Caltech

# Source Controlled Routing

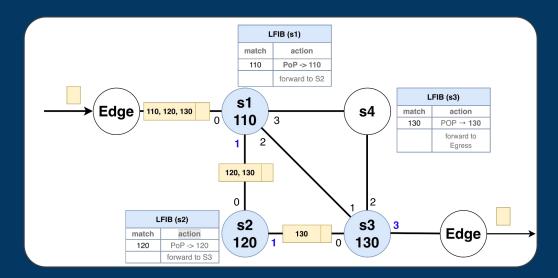

- Traditional way: List-based SR (LSR)

- Path: a list of ports or a stack of labels.

- Edge pushes a stack [110,120,130]

- Each node matches on the top label performs a pop

# Source Routing (SR)

- Traditional way: List-based SR (LSR)

- Path: a list of ports or a stack of labels.

- Each node performs a pop.

# Edge 110, 120, 130 0 s1 110 3 s4 1 2 120, 130 0 130 S2 120 1 130 0 130 Edge

### • Limitations:

- Forwarding state in the packet & rewrite operation (push/pop/swap)

- Variable size of headers that affects the number of encoded hops

- Not fully stateless, still rely on per-node forwarding tables in the core

- MPLS LFIB lookup (match on top label), SR SIDs, BIER forwarding tables.

# Agenda

- Motivation

- Proposal

- Design

- Prototype

- Applications

- Conclusions and future works

# PolKA Proposal

- PolKA: Polynomial Key-based Architecture for High-Performance WAN

- <u>NetSoft 2020 conference paper</u>

- Polynomial Residue Number System (RNS) (Shoup, 2008)

- Chinese Remainder Theorem (CRT)

- Forwarding based on an arithmetic operation: remainder of division

- Path is encoded in a route label.

- Each node decodes its next hop with its own key.

# PolKA Proposal

Aims to design an SR approach to meet the requirements

topology agnostic

fixed header

encoded path

no tables in the core

Deployable in programmable switches

# Agenda

- Motivation

- Proposal

- Design

- Deployment

- Demonstration

- Conclusions

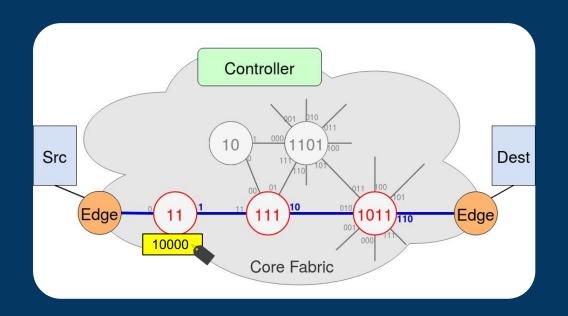

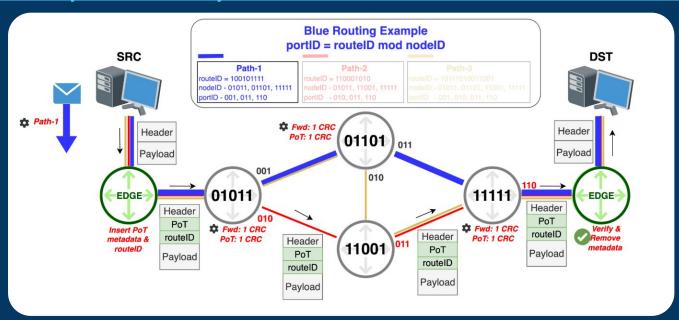

- Three polynomials:

- routeID: a route identifier calculated using the CRT.

- nodeID: to identify each core node.

- Irreducible polynomial

- o **portID**: to identify the ports of each core node.

- The forwarding uses a *mod* operation (remainder of division):

portID = <routeID>

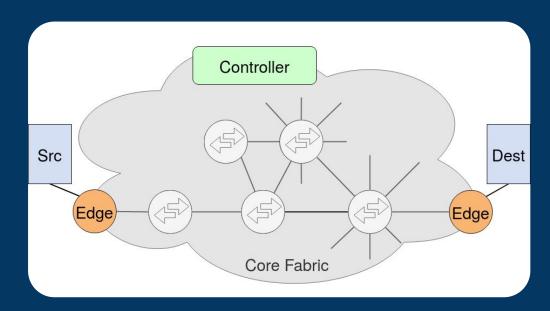

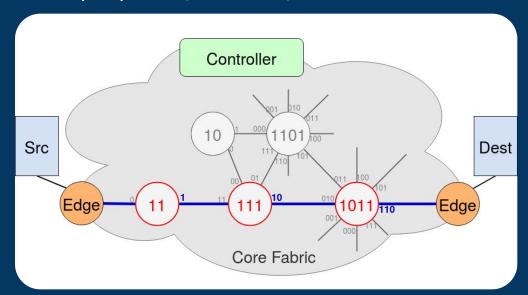

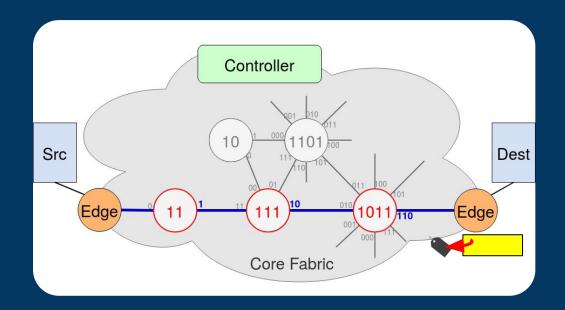

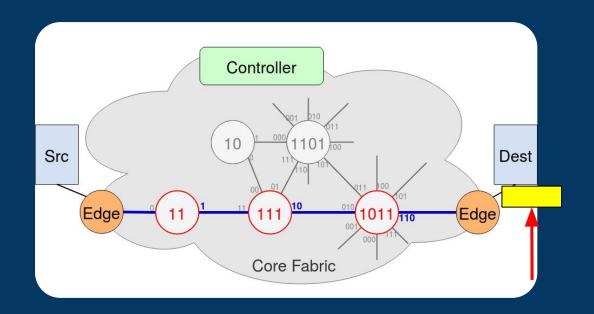

Hosts are connected to edge switches. Edge

Edges are connected to a fabric of core switches.

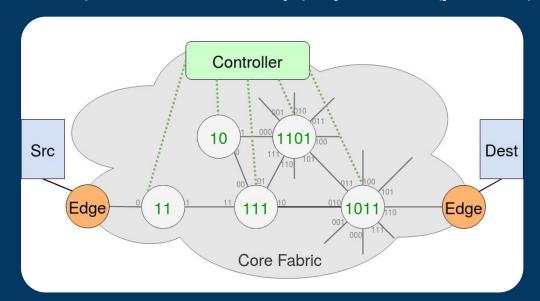

- In a network configuration phase, the Controller assigns irreducible polynomials to core switches (nodelDs).

- Port labels are represented as binary polynomials (portIDs).

- The **Controller** chooses a **path** for a specific flow (proactively or reactively):

- A set of switches: {0011, 0111, 1011}

- o and their output ports: {1, 10, 110}

- The **Controller** chooses a **path** for a specific flow:

- A set of switches: {0011, 0111, 1011}

- and their output ports: {1, 10, 110}

### nodeID polynomials

$$s_1(t) = t + 1 = 11$$

$$s_2(t) = t^2 + t + 1 = 111$$

$$s_3(t) = t^3 + t + 1 = 1011$$

### portID polynomials

$$o_1(t) = 1$$

$$o_2(t) = t = 10$$

$$o_3(t) = t^2 + t = 110$$

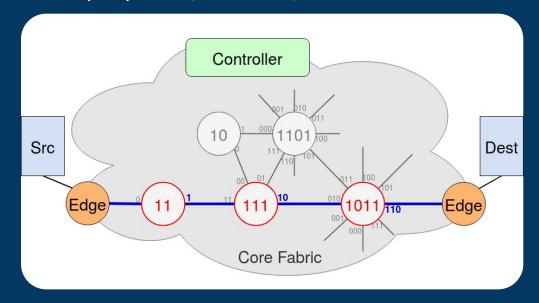

The Controller calculates the routeID using CRT:

$$\circ$$

Complexity:  $O(len(M)^2)$ , where  $M(t) = \prod_{i=1}^n s_i(t)$

N = number of hopsM = product of nodeIDs

The routeID (X) is the result of congruent system in GF(2)

$$001 = X \mod 0011$$

$$010 = X \mod 0111$$

$$110 = X \mod 1011$$

R = 10000

routeID

# Caltech

### nodeID polynomials

$$s_1(t) = t + 1 = 11$$

$s_2(t) = t^2 + t + 1 = 111$

$s_3(t) = t^3 + t + 1 = 1011$

### portID polynomials

$$o_1(t) = 1$$

$o_2(t) = t = 10$

$o_3(t) = t^2 + t = 110$

### Calculate routeID with CRT

$$t^{4} \equiv 1 \mod (t+1)$$

$$t^{4} \equiv t \mod (t^{2}+t+1)$$

$$t^{4} \equiv (t^{2}+t) \mod (t^{3}+t+1)$$

$$t^{4} \equiv 10000$$

The Controller calculates the routeID using CRT:

$$\circ$$

Complexity:  $O(len(M)^2)$ , where  $M(t) = \prod_{i=1}^{N} s_i(t)$

R = 10000

### routeID

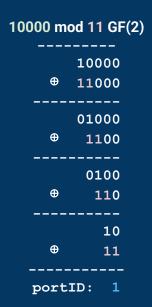

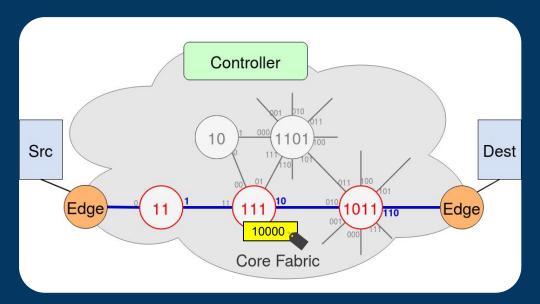

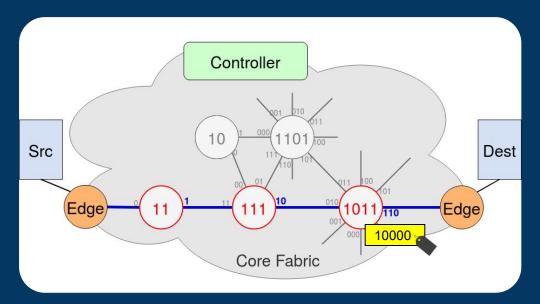

Forwarding operations along the path :

001 =

$$\langle 10000 \rangle_{0011} \rightarrow 10000 \mod 0011$$

010 =  $\langle 10000 \rangle_{0111} \rightarrow 10000 \mod 0111$

110 =  $\langle 10000 \rangle_{1011} \rightarrow 10000 \mod 1011$

# Caltech

### nodeID polynomials

$$s_1(t) = t + 1 = 11$$

$s_2(t) = t^2 + t + 1 = 111$

$s_3(t) = t^3 + t + 1 = 1011$

### portID polynomials

$$o_1(t) = 1$$

$$o_2(t) = t = 10$$

$$o_3(t) = t^2 + t = 110$$

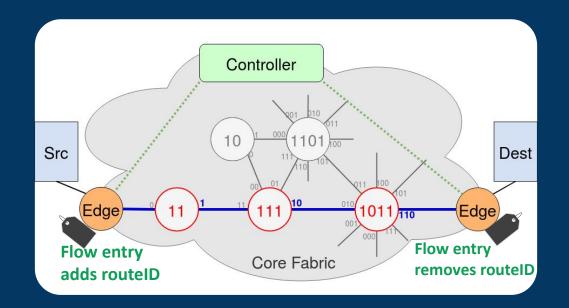

### Calculate routeID with CRT

$$t^{4} \equiv 1 \mod (t+1)$$

$$t^{4} \equiv t \mod (t^{2}+t+1)$$

$$t^{4} \equiv (t^{2}+t) \mod (t^{3}+t+1)$$

$$t^{4} = 10000$$

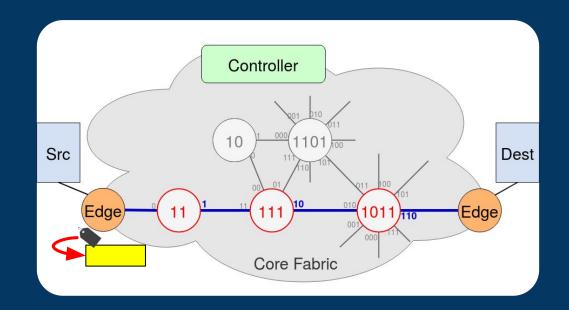

The Controller installs flow entries at the edges to add/remove routeIDs.

When packets arrive, an action at ingress embeds routeID into the packets.

- Forwarding using **mod** operation:  $<10000>_{0011} = 1 \rightarrow \text{output port}$

- No routeID rewrite! No tables in the core nodes!

- Forwarding using **mod** operation:  $\langle 10000 \rangle_{0111} = 10 \rightarrow \text{output port}$

- <No routeID rewrite! No tables!</p>

- Forwarding using **mod** operation:  $<10000>_{1011} = 110 \rightarrow output port$

- <No routeID rewrite! No tables!</p>

Finally, an action at edge egress node removes routeID.

Packet is delivered to the application in a transparent manner.

# How to Implement a *mod* Efficiently in Data Plane?

- P4 language does not natively support the mod operation.

- By using CRC (Cyclic Redundancy Check), we can calculate the mod.

- The Tofino Native Architecture (TNA) supports custom CRC polynomials.

- MOD = 2 SHIFTs + 1 CRC + 2 XORs

**1.** G = nodeID = **01011**, portanto

$$r = deg(G) = 3$$

**2.** D = routeID

$$\div$$

2<sup>r</sup> = 100101444 >> **3** = 100101 (SHIFT RIGHT)

3. dif = routeID - D ·

$$2^r$$

= 100101111  $\oplus$  (100101 << 3)

= 100101111  $\oplus$  100101000 = 111 (SHIFT LEFT, XOR)

**4.**

$$R = \langle D \cdot 2^r \rangle_G = \langle 100101000 \rangle_{(01011)} = 110$$

(CRC)

**5.** portID = dif

$$\oplus$$

R = 111  $\oplus$  110 = 001 (XOR)

# Is PolKA Scalable?

### **Table-based SDN**

# Is PolKA Scalable?

- Number of flow entries:

- Communication states stored only at the edges for encapsulation

- No need to update all the tables along the path

### **Table-based SDN**

### **PolKA**

Caltech

# Is PolKA Scalable With the Number of Nodes?

Length of the routeID: len(R)

$$len(R) \leq \sum_{i=1}^{N} degree(s_i)$$

Where:

$$R = Route$$

$$N = Number of hops$$

$$s_i = nodeID polynomial$$

- We select nodeIDs with the lowest possible degree

- Worst case for data center and WAN topologies (<u>NetSoft 2020</u>)

Caltech

# Is PolKA Scalable With the Number of Nodes?

- Length of the *routeID*: *len(R)*

- We select nodeIDs with the lowest possible degree

- Worst case for data center and WAN topologies (<u>NetSoft 2020</u>)

| Topology          | nports | diam. | size | len(R)    |

|-------------------|--------|-------|------|-----------|

| Two-tier S16 L16* | 24     | 3     | 32   | 21        |

| Fat-tree 16 pods  | 16     | 5     | 320  | <i>55</i> |

| ARPANET           | 4      | 7     | 20   | 42        |

| GEANT2            | 8      | 7     | 30   | 49        |

In practice, the implementation is linked to CRC 8, 16 or 32.

# Is PolKA Scalable With the Number of Nodes?

| Polynomial | Number of irreducible |  |

|------------|-----------------------|--|

| degree     | polynomials           |  |

| 8          | 30                    |  |

| 16         | 4080                  |  |

| 32         | 134,215,680           |  |

CRC degree must provide enough irreducible polynomials to represent all nodes in the topology

# Comparison to existing protocols

PolKA (RouteID length) = CRC<sub>degree</sub> \* hops

| Scheme        | Unit size<br>(per hop) | Example of overhead (10 hops) |

|---------------|------------------------|-------------------------------|

| MPLS          | 4 B                    | 10 labels = 40 Bytes          |

| SR-MPLS       | 4 B                    | 10 segments = 40 Bytes        |

| SRv6          | 16 B                   | 10 segments = 160 Bytes       |

| PolKA (CRC16) | 2 B                    | 10 hops = 20 Bytes            |

| PolKA (CRC32) | 4 B                    | 10 hops = 40 Bytes            |

# Agenda

- Motivation

- Proposal

- Design

- Deployment

- Demonstration

- Conclusions

## Timeline

PolKA received the 2021 **Google Research Scholar Award**

PolKA received the Intel **Connectivity Research Grant (Fast** Forward Initiative)

PolKA@pangr

**IETF 113**

PolKA@panrg **IETF113**

2020

2021

2022

2023/2024

PolKA paper

IEEE NetSoft

Novel Polynomial RNS-based SR and reuse of CRC hardware

**Emulated** prototype in Mininet

ONDM paper Deploy @RARE

Tofino

Emulated prototype Hardware prototype in in FreeRtr &

> Hardware prototype in Tofino w/ FreeRtr control plane

Integration

RARE+FreeRtr

PolKA data &

control plane

integration

implementation +

Extension to multipath SR for reliable communications

M-PolKA paper **IEEE TNSM**

> Lightning Talk Path Aware Networking RG

PolKA@Global P4 Lab

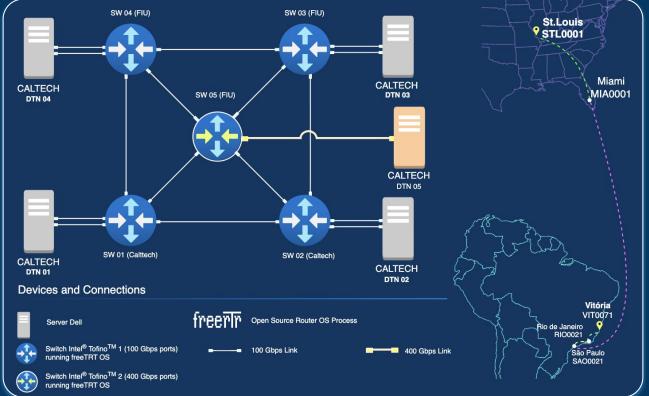

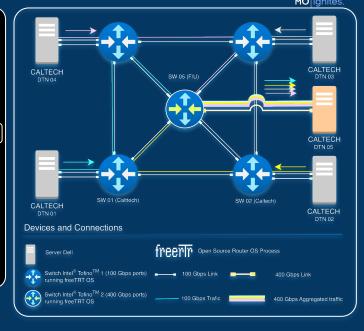

PolKA deployment @Caltech SDN Lab

PolKA Demo at SC-22

**INT-PolKA** paper AINA

Extension to inband network telemetry

PoT-PolKA paper IEEE NetSoft/TNSM

Extension to proof-of-transit

PolKA Al paper Indis

Extension to data science scenario with Al control plane

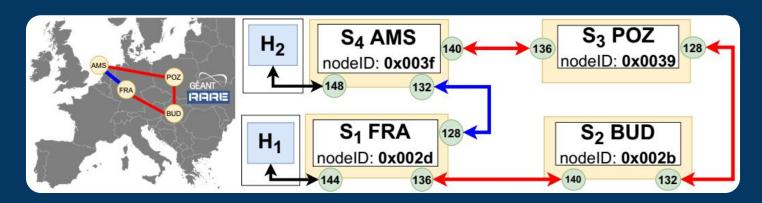

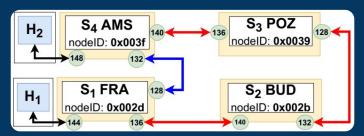

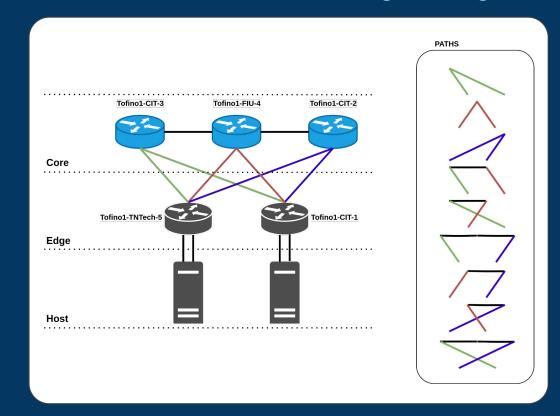

## PolKA: Data Plane Prototype

- P4 language and high-performance Tofino switch

- Deployment: GEANT P4 Lab testbed

- Hardware comparison with list-based and table-based approaches

- Results: ONDM 2021 conference paper

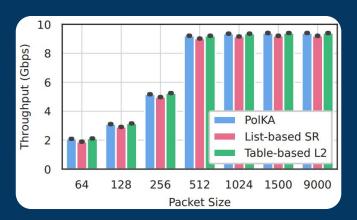

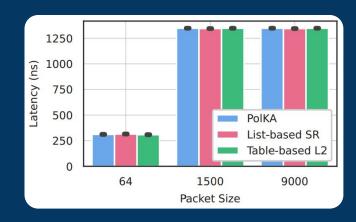

## Experiments

- Throughput (S1-S2-S3-S4):

- High throughput and pps rates

PolKA's performance matches traditional approaches.

- Forwarding Latency:

- Use of hardware timestamps

### PolKA Integrated in *freerTr* and Deployed at Global P4 Testbed

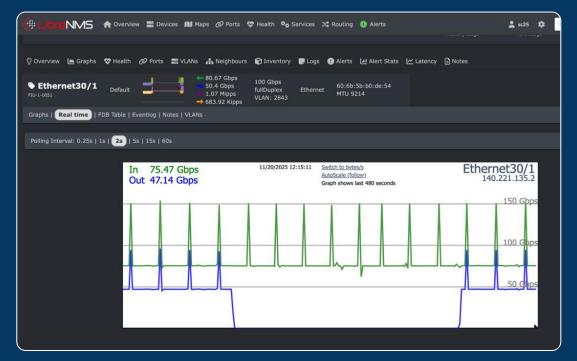

### PolKA Demo@SC2023

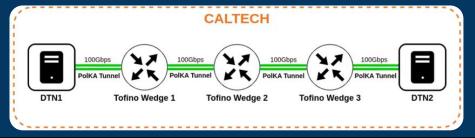

- High Throughput Transfers achieving 100 Gbps line speed

- Caltech P4 lab testbed

- Multiple TCP aggregate

over PolKA tunnels

## Agenda

- Motivation

- Proposal

- Design

- Prototype and Demonstrations

- Use Case : Vera Rubin Observatory

- Conclusions and future works

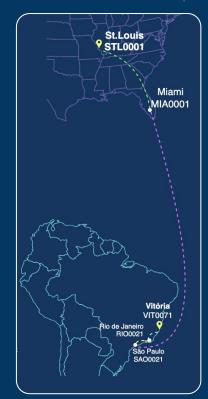

## Use Case: The Vera Rubin Observatory

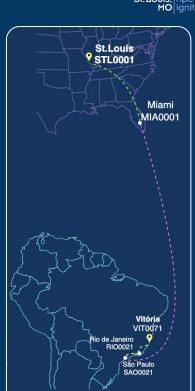

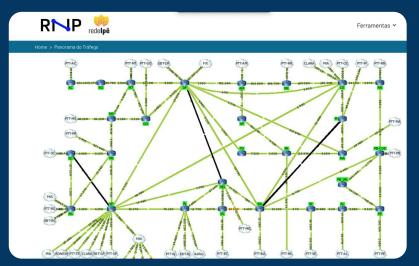

- This is a collaborative use case (Amlight+Caltech+UFES+IFES)

- The telescope delivers 13 GB astronomical images every 27 seconds from Chile to the US Data Facility at SLAC

- Challenges:

- RTT from the Summit to the USDF is approximately 200+ ms

- 0.0001% of packet loss will compromise the Rubin Observatory application

- PolKA was adopted in the Amlight pipeline

Image from Amlight

Caltech

| Total              | ×                   | Tx   |                | Rx           |                     | iface            |

|--------------------|---------------------|------|----------------|--------------|---------------------|------------------|

| ======<br>).00 b/s | =========<br>s 0.00 | b/s  |                | =====<br>b/s |                     | lo:              |

| 0.00 b/s           | 0.00                | b/s  | 0.00           | b/s          | 0.00                | enp33s0f0:       |

| .73 Gb/s           | s 239.73            | Gb/s | 97.09          | Gb/s         | 142.64              | enp193s0np0:     |

| 0.00 b/s           | 0.00                | b/s  | 0.00           | b/s          | 0.00                | enp161s0np0:     |

| 0.00 b/s           | 0.00                | b/s  | 0.00           | b/s          | 0.00                | vlan1321:        |

| 0.00 b/s           | 0.00                | b/s  | 0.00           | b/s          | 0.00                | docker0:         |

| 0.00 b/s           | 0.00                | b/s  | 0.00           | b/s          | 0.00                | enp161s0np0.100: |

| 0.00 b/s           | 0.00                | b/s  | 0.00           | b/s          | 0.00                | enp161s0np.2830: |

| .73 Gb/s           | s 239.73            | Gb/s | 97 <b>.</b> 09 | Gb/s         | <br>142 <b>.</b> 64 | total:           |

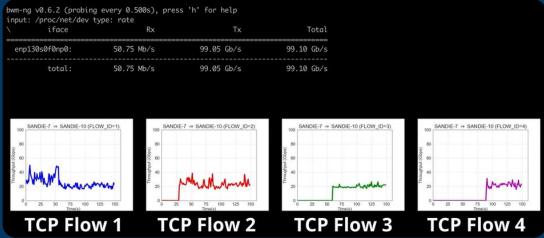

New deployment in Tofino 2 switches

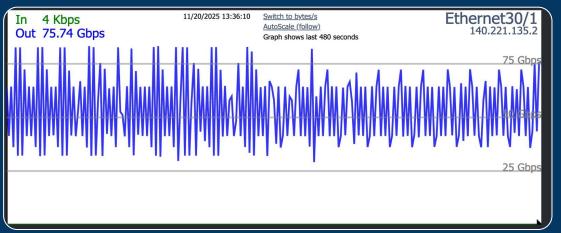

PolKA delivers a line rate throughput at the Caltech Booth@SC25

Caltech

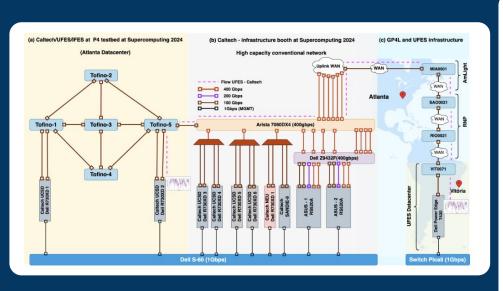

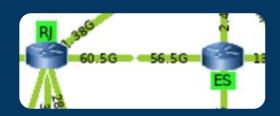

PolKA delivered 5 times more throughput than SC24 achieving high-performance at long distance from <u>Caltech Booth@SC25 to UFES</u> via Amlight and RNP

Caltech

Miami MIA0001

St.Louis

| bwm-ng v0.6.2 (probing every 0.500s), press 'h' for help<br>input: /proc/net/dev type: rate |           |            |           |            |  |  |  |  |

|---------------------------------------------------------------------------------------------|-----------|------------|-----------|------------|--|--|--|--|

| 1                                                                                           | iface     | Rx         | Tx        | Total      |  |  |  |  |

|                                                                                             | enp3s0f1: | 54.18 Gb/s | 9.44 kb/s | 54.18 Gb/s |  |  |  |  |

|                                                                                             | total:    | 54.18 Gb/s | 9.44 kb/s | 54.18 Gb/s |  |  |  |  |

PolKA delivered 5 times more throughput than SC24 achieving high-performance at long distance from <u>Caltech Booth@SC25 to UFES</u> via Amlight and RNP

Caltech

RIO0021

VIT0071

PolKA delivered 5 times more throughput than SC24 achieving high-performance at long distance from <u>Caltech Booth@SC25 to UFES</u> via Amlight and RNP

### Takeaway Message of PolKA Approach 1/2

- PolKA delivers a high-performance network solution by reusing CRC hardware.

- Supports line rate performance of packet forwarding in programmable Switches

- Validated at multiple testbeds with 10 Gbps, 100 Gbps, and .. 400 Gbps

- Demonstrations at SC2022, SC2023, SC2024 and SC2025

## Recap of demonstrations Caltech@SuperComputing

- Big data streams at line rate 100 Gbps

- PolKA@ Caltech P4 lab testbed

- Multiple aggregated traffic flows transported by PolKA tunnels

- Multiple big data streams achieving 200 Gbps

- o PolKA@ Caltech P4 lab testbed at the SC 23

- Novelty to be demonstrated:

- Path aware networking for data intensive traffic flows with highly adaptable, dynamic traffic steering and agile path reconfiguration

- Traffic engineering with *optimal traffic flow* allocation

- Vera Rubin Observatory (VRO) Use Case

- Intradomain traffic at ~250 Gbps in Programmable Dataplanes

Caltech

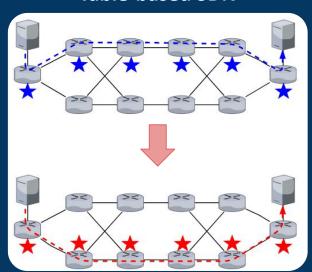

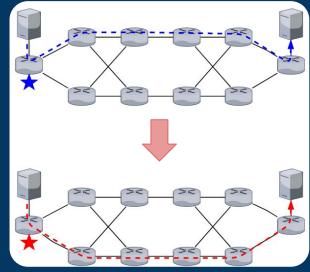

### Takeaway Message of PolKA Approach 2/2

Network scalability

Granularity

Agility

Only at the Edges

Fine granularity

Low latency

- Scalable: Network state is defined only at the edges

- Stateless core with tableless nodes enables the selection of any path (fine granularity to assign flows and allows TE optimization)

- Low latency on path configuration by updating a single table entry at the edge

Caltech

#### Applications in different domains

- Security: Sovereign paths

- Paths with a proof-of-transit signature

- Telefonica is interested in path anonymization properties (e.g ToR)

#### CRC4EVER Demo at Sigcomm 2025

#### CRC4EVER: Cyclic Redundancy Check for Enhanced Verification and Efficient Routing

PathSec: Path-Aware Secure Routing with Native Path Verification and Auditability

Authors: M. Martinello and Everson Borges et al. IEEE SDN NFV 2024

### Applications in different domains

- Security : Sovereign paths

- Paths with proof-of-transit signatures integrated in a blockchain

- Telefonica is interested in path anonymization properties (e.g ToR)

- 5G transport network : slices with stringent performance guarantees

- Ongoing initiative with Open RAN Brazilian Program

- Brazilian telecom agency regulator (Anatel) is giving us support

- HPC: PolKA Architecture design based on fabric stateless core with edges

- High performance ethernet alternative to infiniband

#### HPC use case: PolKA design based on stateless core fabric with edge intelligence

- PolKA provides a path controlled at the edge to:

- Any nic, any GPU

- Investigate the deployment in broadcom chips

- Trident4/X has a NPL/P4 pipeline

- Jericho 2

#### Standardization and Commercialization: Looking for partners

- Technologies are formally registered at INPI

- Looking for partners to support the standardization, integration, and commercialization.

- We invite institutions and companies to co-develop, scale and create new solutions with us.

Data de Publicação: 24/01/2023

Data de Criação: 24/01/2023

Data de Criação: 24/01/2023

- § 2º do art. 2º da Lei 9.609/98: "Fica assegurada a tutela dos direitos relativos a programa de computador pelo prazo de cinquenta anos contados a partir de 1º de janeiro do ano subsequente ao da sua publicação ou, na ausência desta, da sua criação"

Título: POLKA: ARQUITETURA BASEADA EM CHAVES POLINOMIAIS PARA ROTEAMENTO DE ORIGEM EM REDES PROGRAMÁVEIS

Algorítimo hash: SHA-512 - Secure Hash Algorithm

Resumo digital hash: 8bce9214b6caf23d8b7fdb103c8d2b3dddf58c76de859a602c595d1ea a2f0ab838e463ca4tf8dragh330154f63a26ec0cf7a92b8b0aa0668a07

Data de Publicação: 24/01/2023

Data de Criação: 24/01/2023

- § 2º do art. 2º da Lel 9.609/98: "Fica assegurada a tutela dos direitos relativos a programa de computador pelo prazo de cinquenta anos contados a partir de 1º de janeiro do ano subsequente ao da sua publicação ou, na ausência desta, da sua criação"

Título: INNETMOD: HABILITAÇÃO DA OPERAÇÃO DA DIVISÃO POLINOMIAL DA ARITMETICA MODULAR POR MEIO DA VERIFICAÇÃO CÍCLICA DE REDUNDÂNCIA (CRC) EM PROCESSADORES DE PACOTES PROGRAMÁVEIS

Algorítimo hash: SHA-512 - Secure Hash Algorithm

Resumo digital hash: 767219631d686334e269e62d89d31e6ee2f72e571a8350eca60b13 ce38a460aea646521d84ba20ba84bae01b8763d401b7ea27a5826d0 7d31fc43dcddfc3d

Data de Publicação: 24/01/2023

Data de Criação: 24/01/2023

- § 2º do art. 2º da Lel 9.609/98: "Fica assegurada a tutela dos direitos relativos a programa de computador pelo prazo de cinquenta anos contados a partir de 1º de janeiro do ano subsequente ao da sua publicação ou, na ausência desta, da sua criação"

Título: M-POLKA: ROTEAMENTO DE ORIGEM POR MÚLTIPLOS CAMINHOS EM REDES PROGRAMÁVEIS

AlgorítImo hash: SHA-512 - Secure Hash Algorithm

4eebae700b70ef

Resumo digital hash: 633315f2484b83bac5373c534cae6c61257241aa2411dc49d08b1162 4c032f5aZaf9331b8e6a46000b42b29cfd49267e1b3790451690347a9 bda63945640cf08

## Acknowledgments

- The framework provided by the GNA-G and the whole ecosystem of NRENs (Global P4 Lab) enabled the PolKA routing to be tested thanks to:

- GNA-G Data Intensive Science WG

- GNA-G AutoGOLE / SENSE WG

- GEANT RARE Project

- ... And all it's collaborating institutions and teams

- TO NONHOUSE SEED OF STANKE SEED OF S

- Collaboration with Caltech is crucial hosting us at the booth

- Provides all the resources (e.g. Tofinos + servers +...) to deploy it in a near production allowing us to demonstrate PolKA in the best conditions

### PolKA Community, Partners and Collaborations

- Caltech: Professor Harvey Newman and Raimondas Širvinskas

- RARE GÉANT: Frédéric Loui, Csaba Mate, Eoin Kenny

- RNP: Marcos Schwarz

- Qualcomm: Jordi Ros Giralt

- Trinity College Dublin (Connect): Marco Ruffini

- CNPq, FAPES and FAPESP-(Brazilian research funding agencies )

- PorVIR 5G and Smartness projet

- 2021 Google Research Scholar Award

- 2022 Intel Connectivity Research Grant (Fast Forward Initiative)

#### Selection of Our Recent Publications

- <u>CRC4EVER: Cyclic Redundancy Check for Enhanced Verification and Efficient Routing</u> (Demo at Sigcomm 2025)

- A Path-Aware Routing for Data Intensive Science: Proposal, Deployment and Evaluation in High-Performance Testbed (WGRS 2025)

- Transport efficiency for data-intensive science: deployment experiences and bottleneck analysis (An. of Telecomm, 2025)

- PINT-BoX: Path-aware networking IN a Tofino BoX (Demo at IEEE NFV/SDN, 2024)

- Framework for Integrating Machine Learning Methods for Path-Aware Source Routing (IEEE INDIS@SC, 2024)

- PathSec: Path-Aware Secure Routing with Native Path Verification and Auditability (IEEE NFV/SDN, 2024)

- PoT-PolKA: Let the Edge Control the Proof-of-Transit in Path-Aware Networks (IEEE TNSM, 2024)

- M-PolKA: Multipath Polynomial Key-based Source Routing for Reliable Communications (IEEE TNSM, 2022)

- <u>Chaining-Box: A Transparent Service Function Chaining Architecture Leveraging BPF</u> (IEEE TNSM, 2021)

- Programmable Switches for in-Networking Classification (IEEE INFOCOM, 2021)

- <u>Deploying PolKA Source Routing in P4 Switches</u> (ONDM, 2021)

- PolKA: Polynomial Key-based Architecture for Source Routing in Network Fabrics (IEEE NetSoft, 2020)

- <u>ProgLab: Programmable labels for QoS provisioning on software defined networks</u> (Computer Communication, 2020)

- KeySFC: Traffic steering using strict source routing for dynamic and efficient network orchestration (Computer Networks, 2020)

- RDNA: Residue-defined networking architecture enabling ultra-reliable low-latency datacenters (IEEE TNSM, 2018)

#### Additional references

- 1. Global Network Advancement Group: Towards a Next Generation System for Data Intensive Sciences

- 2. <u>Documentation: Let's enable PolKA in freeRtr</u>

- 3. PolKA presentation at Google Research Scholar Award

- 4. Multipath PolKA presentation at ONF 2022

- 5. PolKA github

- 6. RARE website

- 7. <u>FreeRouter website</u>

- 8. <u>LabNERDS Videos</u>

- 9. PolKA NetSoft 2020 conference paper

- 10. V. Shoup, A computational introduction to number theory and algebra, 2008.

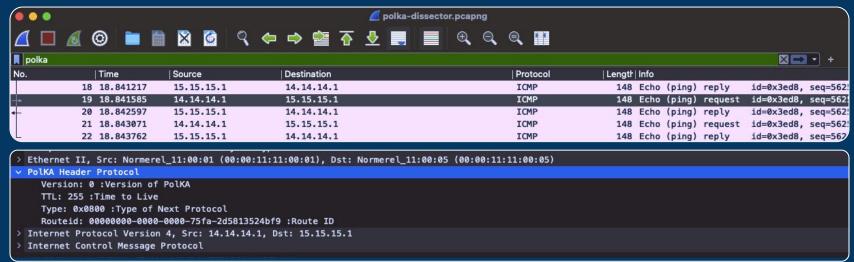

#### PolKA: Github

- https://nerds-ufes.github.io/polka/

- References

- Tutorials (Mininet and FreeRouter)

- Wireshark dissector

- More to come...

# Thank you for attention!

**Everson Scherrer Borges**

everson@ifes.edu.br

\* This work was a recipient of the 2021 Google Research Scholar and the 2022 Intel Connectivity Research Grant (Fast Forward Initiative) Awards, and Received funds from CAPES (Finance Code 001), CNPq, FAPESP, FAPES, CTIC, and RNP.

## Ok... Why should I use PolKA?

- One good reason...

- ... It is easy to setup paths/tunnels!

- It has some interesting properties that enable innovative applications.

- Ex: multicast communication model support, multipath routing, failure protection, Proof of Transit, telemetry...

- Open source implementation in software and in hardware

- RARE/FreeRtr